Features/Machines/Edison: Difference between revisions

Choonho.son (talk | contribs) |

Choonho.son (talk | contribs) |

||

| Line 22: | Line 22: | ||

== Description == | == Description == | ||

=== Hardware features === | |||

{| | |||

| '''Component''' || '''Description''' | |||

|- | |||

| Processor || 22 nm Intel® SoC that includes a dual-core, dual-threaded Intel® Atom™ CPU at 500 MHz and a 32-bitIntel® Quark™ microcontroller at 100 MHz | |||

|- | |||

| RAM || 1 GB LPDDR3 POP memory (2 channel 32 bits @ 800 MT/sec) | |||

|- | |||

| Internal storage || 4 GB eMMC (v4.51 spec) | |||

|- | |||

| Power || TI SNB9024 power management IC | |||

|- | |||

| Wireless || Dual-band (2.4 and 5 GHz) IEEE 802.11a/b/g/n | |||

|- | |||

| Bluetooth || BT 4.0 + 2.1 EDR | |||

|- | |||

| Antenna || Dual-band onboard chip antenna or u.FL for external antenna | |||

|- | |||

| Connector || 70-pin Hirose DF40 Series (1.5, 2.0, or 3.0 mm stack height) | |||

|- | |||

| Size || 35.5 × 25.0 × 3.9 mm maximum (to be verified) | |||

|- | |||

| Power input || 3.15 to 4.5 V | |||

|- | |||

| I/O || 40 general purpose GPIO which can be configured as: | |||

• SD card: 1 interface | |||

• UART: 2 controllers (one full flow control, one Rx/Tx) | |||

• I2C: 2 controllers | |||

• SPI: 1 controller with 2 chip selects | |||

• I2S: 1 controller | |||

• GPIO: Additional 14 (with 4 capable of PWM) | |||

|- | |||

| USE 2.0 || 1 OTG controller | |||

|- | |||

| Clock || 19.2 MHz, 32 kHz | |||

|} | |||

== Detailed Summary == | == Detailed Summary == | ||

Revision as of 11:18, 27 May 2015

Summary

Add system emulation of the Intel Edison Compute Module.

Owner

- Name: Choonho Son

- Email: choonho.son@analytaps.net

Challenges

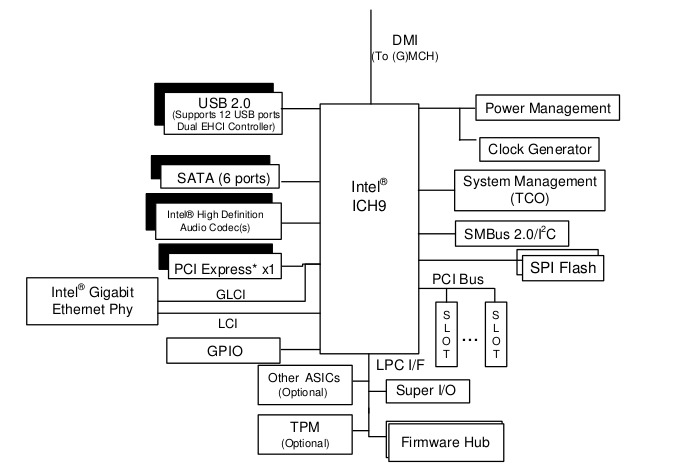

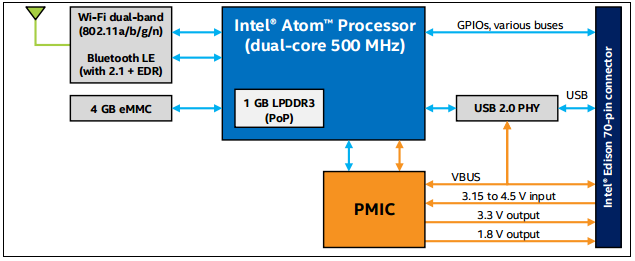

The QEMU support for the PC machine type is fairly poor today. The supported host chipset is I440FX and Q35. Intel Edison Compute Module is SoC with Intel Atom CPU and built-in Bluetooth and Wi-Fi.

ICH9 block diagram

Intel Edison block diagram

Description

Hardware features

| Component | Description |

| Processor | 22 nm Intel® SoC that includes a dual-core, dual-threaded Intel® Atom™ CPU at 500 MHz and a 32-bitIntel® Quark™ microcontroller at 100 MHz |

| RAM | 1 GB LPDDR3 POP memory (2 channel 32 bits @ 800 MT/sec) |

| Internal storage | 4 GB eMMC (v4.51 spec) |

| Power | TI SNB9024 power management IC |

| Wireless | Dual-band (2.4 and 5 GHz) IEEE 802.11a/b/g/n |

| Bluetooth | BT 4.0 + 2.1 EDR |

| Antenna | Dual-band onboard chip antenna or u.FL for external antenna |

| Connector | 70-pin Hirose DF40 Series (1.5, 2.0, or 3.0 mm stack height) |

| Size | 35.5 × 25.0 × 3.9 mm maximum (to be verified) |

| Power input | 3.15 to 4.5 V |

| I/O | 40 general purpose GPIO which can be configured as:

• SD card: 1 interface • UART: 2 controllers (one full flow control, one Rx/Tx) • I2C: 2 controllers • SPI: 1 controller with 2 chip selects • I2S: 1 controller • GPIO: Additional 14 (with 4 capable of PWM) |

| USE 2.0 | 1 OTG controller |

| Clock | 19.2 MHz, 32 kHz |